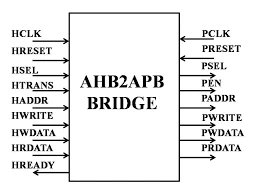

AHB–APB Bridge with Self-Checking Verification

| Repository | Mummanajagadeesh/ahb2apb |

|---|---|

| Start Date | Nov 2025 |

Overview

| Item | Description |

|---|---|

| Type | Parameterizable AHB-Lite → APB Bridge |

| Language | SystemVerilog |

| Verification | Self-checking SV Testbench + Assertions |

| Tools | Icarus Verilog, GTKWave |

RTL Design

- Parameterizable AHB-Lite to APB bridge

- Supports:

- Single read

- Single write

- Burst read

- Burst write

- FSM-based control architecture

- Address and data latching

- Write buffering

- Read-data return path

- Burst sequencing logic

- Handles pipelined and non-pipelined AHB accesses

- Proper transaction-type decoding and continuation handling

Verification Environment

- Fully self-checking SystemVerilog testbench

- Macro-controlled compile-time test modes:

SINGLE_READSINGLE_WRITEBURST_READBURST_WRITE

- Assertion-based protocol validation

- Automatic PASS/FAIL reporting

- Per-test VCD waveform generation

Protocol Coverage

- Verified correctness across:

- All single and burst transactions

- Read/write sequencing

- Address alignment and transfer continuation

- Ensured correct translation from AHB pipelined phase to APB two-phase protocol

Additional Work

Designed and functionally verified standalone peripheral controllers:

I2C Master Controller – Implements a single-master, multi-slave I²C bus supporting standard-mode timings, programmable SCL low/high periods, ACK/NACK handling, and clock stretching detection. Features deterministic START/STOP generation, byte-wise transfers, and address+data framing logic.

SPI Master (Modes 0–3) – Supports CPOL/CPHA mode selection, 8-bit full-duplex transfers, configurable SCLK division, selectable slave-select behavior, and MSB-first shifting. Designed with a compact FSM and separate TX/RX shift registers for predictable cycle behavior.

UART TX Soft-Core IP – Lightweight serial transmitter with baud-rate generator, start/stop framing, data-valid gating, and FIFO-less single-byte serialization. Fully synthesizable and intended as a drop-in peripheral for SoCs, teaching cores, or FPGA peripheral sets.