Verilog HDL Toolkit for Image Processing and Pattern Recognition

IMage PROcessing using VErilog

ImProVe (IMage PROcessing using VErilog) is a project focused on implementing image processing techniques using Verilog. It involves building image processing logic from the ground up, exploring various algorithms and approaches within HDL

View Project

NEural NEtwork in VERilog

Never (NEural NEtwork in VERilog) implements a neural network in Verilog for better hardware acceleration of image processing tasks

View Project

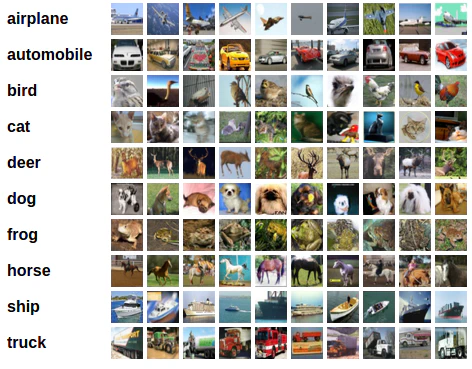

CIFAR10 CNN

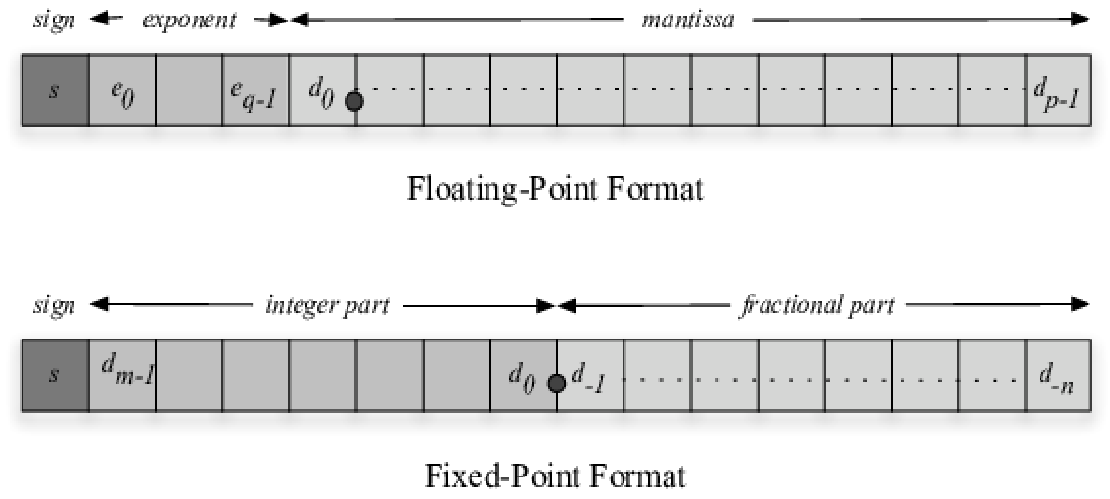

Developed a lightweight CNN [Conv2D×2 + MaxPool]×3 → GAP → Dense(10) for CIFAR-10 Image Classification (32x32RGB) using both IEEE 754 floating-point and Q1.31, Q1.15, Q1.7, and Q1.3 fixed-point arithmetic, achieving 84% accuracy in both implementations (Py ~85% | FP ~84% | Q31 ~84% | Q15 ~84% | Q7 ~82% | Q3 ~65%)

View Project

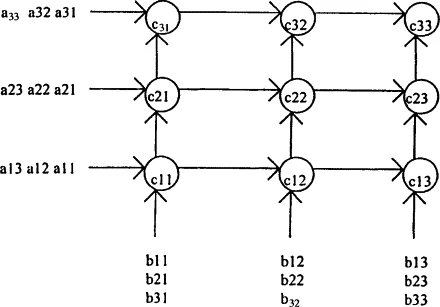

Matrix Multiplier with Systolic Array

Systolic array of MAC PEs with Booth multipliers and carry-save adders, supporting both GEMM and 3×3 CNN convolutions for hardware-accelerated deep learning and linear algebra

View Project

Fixed-Point Conversion Report for EMNIST Neural Network

This report outlines the transition of the EMNIST neural network from floating-point (IEEE754) to fixed-point arithmetic to reduce hardware complexity and improve synthesis compatibility, while aiming to preserve model accuracy

View ProjectNo projects found for the selected tags.

QUICK LOOK AT REPOS

Verilog HDL Toolkit for Image Processing and Pattern Recognition

Duration: Individual, Ongoing

Tools: Verilog (Icarus Verilog) | C++ & Python (OpenCV, NumPy, Tkinter) | Scripting (TCL. Perl)

- Designed

image processing algorithms(e.g., edge detection, geometric & color transforms, noise reduction) in Verilog, utilizinghardware optimized mathtechniques to maximize computational efficiency; fine-tuned forlow-latencypreprocessing in embedded vision SoCs - Implemented a

64-bit3-layerperceptron (MLP 784-256-128-62) for Extended-MNIST Character Recognition (62 classes, ∼124k samples) using FSM-controlled neural network in Verilog; achieved>90% training accuracy(>75% simulation accuracy) with~1.5s inference latency` (in simulation); developed full end-to-end preprocessing and inference workflow - Designed the architecture with a

modular FCNN pipeline, enabling easy expansion or adaptation to otherimage classification tasks; core components (preprocessing, layer ops, controller FSMs) can be reused or scaled for different dataset sizes and class counts - Automated model

inferenceandperformance metricevaluation via Tcl/Perl scripts (py & iverilog commands execution); real-time Tkinter GUI for test user input - Developed a

lightweight CNN [Conv2D×2 + MaxPool]×3 → GAP → Dense(10)forCIFAR-10 Image Classification (32x32RGB)using bothIEEE 754floating-point andQ1.31,Q1.15,Q1.7, andQ1.3fixed-point arithmetic, achieving 84% accuracy in both implementations (Py ~85% | FP ~84% | Q31 ~84% | Q15 ~84% | Q7 ~83% | Q3 ~65%) - Prototyping real life applications including

label detection,document scanning,stereo depth map generation, and neural network inference for MNIST/EMNIST datasets - Currently working on Object Detection using shallow CNNs on the

Pascal VOCdataset.

I highly recommend checking out the main project, as this is just a subset. The main project focuses on image processing algorithms, and working on [ImProVe (IMage PROcessing using VErilog)] has made the learning curve for this project much easier.

[NeVer (Neural Network in Verilog)] is a key subproject within the broader ImProVe initiative. This work focuses on the design and implementation of a fully functional neural network entirely in Verilog, with the objective of optimizing it for efficient hardware acceleration.

Please note that the names of these projects are not meant to be taken too seriously. The names like ImProVe or NeVer may not fully reflect their functions – ImProVe doesn’t actually improve images, but processes them, and NeVer isn’t about something “never-implemented” – many have done it before. The names just make it easier for me to organize folders and code

Tabular Summary of all technical details ( NN Inference Workflow )

| Parameter | Value / Detail | Technical Highlights |

|---|---|---|

| Accuracy | >90% training acc (>70% dev acc) | High classification precision on both MNIST (10 classes) and EMNIST (62 classes). |

| Verilog Simulation Accuracy | >75% (tested on 1000 random samples); >65% for fixed point precision | Accuracy observed when predicting directly using Verilog simulation with fixed-point arithmetic. |

| Inference Latency | ~1.5 sec per prediction (tested on 1000 random samples) | Achieved via a tightly controlled FSM-driven sequential evaluation in simulation. |

| Pipelining | Coarse-grained | Finite State Machine (FSM) orchestrates layer-by-layer processing without fine-grained, parallel overlap. |

| Data Type | IEEE 754 real as well as fixed-point | Simulation relies on IEEE 754 floating-point (non-synthesizable) for high-precision computation during development. |

| Python Libraries | NumPy exclusively | Utilizes NumPy for all training routines and parameter extraction, without relying on higher-level ML frameworks. |

| Dataset | EMNIST ByClass ≈124k (≈2K per class, 62 classes); MNIST – TSD (Google Colab) | Separate datasets: EMNIST ByClass, with 62 classes (digits and both uppercase and lowercase letters), and MNIST (handwritten digits 0-9), trained independently for alphanumeric character recognition tasks. |

| Training Optimizers | Adam (1500 iterations) + SGD with Momentum (500 iterations) | Hybrid optimization: Adam for rapid convergence initially, then SGD with Momentum for fine-tuning and refinement. |

| Neural Architecture (MNIST) | 784 (input) – 128 (hidden) – 10 (output) | A compact feed-forward architecture optimized for digit recognition. |

| Neural Architecture (EMNIST) | 784 (input) – 256 (hidden) – 128 (hidden) – 62 (output) | Expanded design to support 62 classes (digits, uppercase, lowercase) within the same inference infrastructure. |

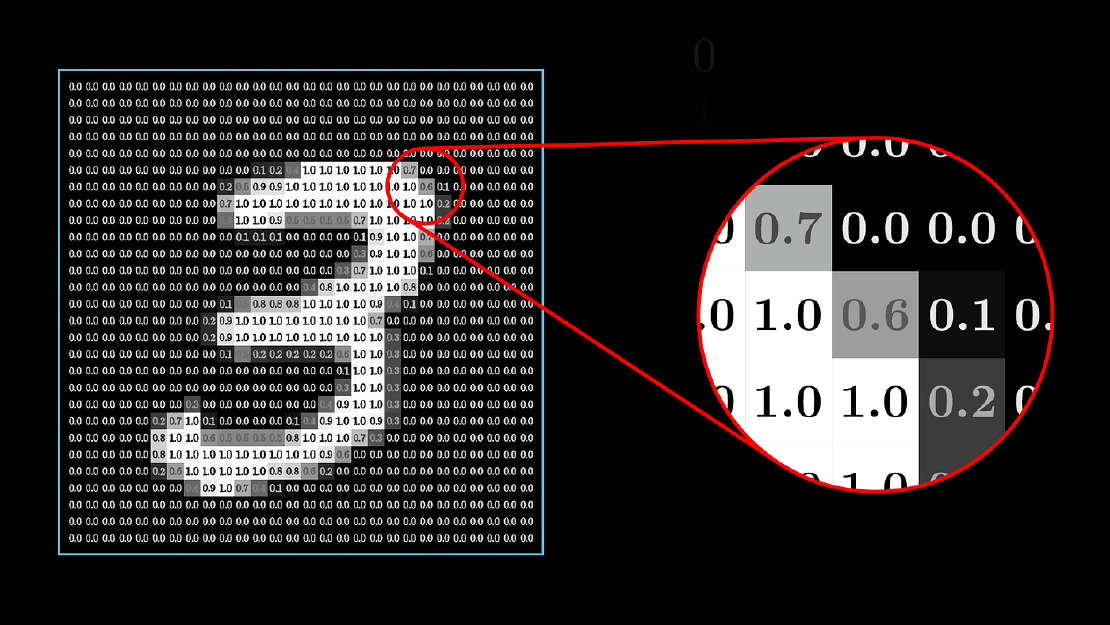

| Weight & Bias Scaling | ×2^13 | Parameters are uniformly scaled to simulate fixed-point arithmetic for Verilog inference compatibility. Minor differences in absolute scale are absorbed by activation functions, so relative scaling has minimal impact on overall network behavior |

| Input Image Format | 28×28 grayscale | Images are captured via a Tkinter drawing interface, then saved as 600x600 rgb image. |

| Preprocessing Pipeline | Custom C++/Python scripts for initial image conversion + Verilog modules | Workflow includes image conversion (img2bin.py), image processing (resize, contrast, gray, roi, padding, invert, rotate, flip, flatten), and file preparation for memory module generation. |

| Memory Module Generation | C++/Python scripts (wtbs_loader.py, memloader_from_inp_vec.py) | Automated conversion of weight, bias, and image vector files into synthesizable Verilog memory modules. |

| Simulation Environment | Icarus Verilog | Compilation and simulation are conducted using Icarus Verilog with dedicated testbenches for module validation. |

| Automation & Workflow | Fully automated, cross-platform | Integration via Makefiles (Linux/macOS), batch scripts (Windows), plus Perl and TCL scripts to streamline build, test, and simulation phases. |

| Verification & Testbenches | Implemented | Robust testbenches facilitate both unit-level and end-to-end verification of the Verilog inference modules. |

| System Integration | End-to-End pipeline | Seamless integration connects Python for image input/output with Verilog for core logic simulation, creating a unified hardware prototyping workflow |

| Test User Interaction | Tkinter-based interface | Direct interactive drawing capability allows real-time testing of handwritten inputs through the complete conversion and inference flow. |